Assignment Details:

- In this Problem you are to perform spectral analysis on the audio signals You are given a short piano piece “piano_sequence.wav” of duration 3 measures. The second musical note and first chord (combination of notes) are given separately in “piano_single_note.wav” and “piano_chord.wav” respectively.

Write a MATLAB program to perform the followings:

- Read “piano_single_note.wav” into a vector

- Determine the sampling rate and number of samples in

- Use MATLAB built-in function to perform DFT on x, and save the result in

- Create an array freq (in Hz) that represents the actual frequencies corresponding to the indices of

- Plot the |X(f)| vs freq from 0Hz to 3kHz.

- From the spectrum, determine the fundamental frequency and its harmonics of the single

- Repeat the same spectra analysis for “piano_chord.wav”, including plotting

|X(f)| vs freq.

- From the spectrum of “piano_chord”, group the fundamental frequency and it harmonics that belong to the same musical Determine the fundamental frequency of each note.

- Exporting your filter designs in 4(a) and 4(b) to

In SIMULINK, create two discrete-time signals x1[n], x2[n] supposition with a band limited white noise as follow:

Tc = 0.000021 sec

noise power: 0.0000021

x1[n] = sin(2nf1nTc) + noise, f1 = 3kHz x2[n] = sin(2nf2nTc) + noise, f2 = 12kHz

Submit the circuit diagrams that show the connections of the discretised signal source, band limited white noise source, digital filters, and the scope capturing the input and output signals.

Plot the input and output signals in the time-domain before and after the filters, for all 4 cases (2 signals x 2 filters). From the filter design frequency response, estimate the attenuation expect at 3kHz and 12kHz.

Comment on the waveforms.

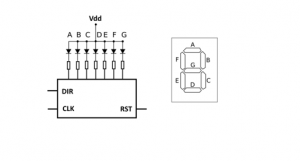

- Write a VHDL code to implement the circuit function described

The circuit is to display the last four digits of your student ID number on a 7-segment display, one digit at a time, triggered by the falling edge of the clock signal.

DIR: Direction of the display sequence, ‘1’ = forward, ‘0’ = reverse. CLK: clock pulse for the display sequence.

RST: reset the display counter.

ID number is 3313, the last four digits are ‘3’, ‘3’, ‘1’, ‘3’, and the circuit is to display ‘3’, ‘3’, ‘1’, ‘3’,’3’, ‘3’,’1’,’3’…when DIR = ‘1’ and display

‘3’,’3’,’1’,’3’,’3’,’3’,’1’,’3’,’3’…when DIR = ‘0’.

Code must be well-organized and clearly explained.

Write a small test bench code to perform the simulation and verification.

Submit your VHDL code, test bench code and the simulation waveforms.

Hire a Professional Essay & Assignment Writer for completing your Academic Assessments

Native Singapore Writers Team

- 100% Plagiarism-Free Essay

- Highest Satisfaction Rate

- Free Revision

- On-Time Delivery

SingaporeAssignmentHelp.com delivers excellent my assignment help services for all the students studying in diverse Singaporean universities and colleges. Our writers are prominent in all the sphere of studies and offer you cheap assignment writing help services.

Looking for Plagiarism free Answers for your college/ university Assignments.

- MGE302 Applied Economics Individual Assignment 2026 | SIM

- POL351 Comparative Politics in Southeast Asia End-of-Course Assessment 2026 | SUSS

- SOC313 Sociology of Education End-of-Course Assessment 2026 | SUSS

- BPM213 Procurement Management Tutor-Marked Assignment 2, 2026 | SUSS

- MNGT3013 Innovation Management Assessment 1, 2026 | University of Newcastle

- BPM203 Construction Project Management Group-based Assignment 01, 2026 | SUSS

- BUS353 Project Management End-of-Course Assessment 2026 | SUSS

- BUS357 Starting and Managing a Business End-of-Course Assessment 2026 | SUSS

- EA301MAA Airline Route and Fleet Planning Individual Assignment 2026 | EAU

- BUS354 Customer Relationship Management Assignment Question 2026 | SUSS